# **A Novel Nine Level Inverter For Photovoltaic Applications**

E.G.Chinju<sup>1</sup>, S.Reshmila<sup>2</sup>

<sup>1</sup>(Dept. of EEE, Sree Narayana Gurukulam College of Engineering, Kolenchery, Ernakulum, Kerala, India) <sup>2</sup>(Dept. of EEE, Sree Narayana Gurukulam College of Engineering, Kolenchery, Ernakulum, Kerala, India)

**Abstract**: This paper proposes a new Nine Level Inverter for a photovoltaic system. The nine- level inverter is configured using a capacitor selection circuit and a full-bridge power converter, connected in cascade. Since the output of PV array is very low, a DC –DC converter is used to boost the output of PV array. The DC-DC power converter consists of DC-DC boost converter and a transformer to convert the output voltage of the PV array into three independent voltage sources with multiple relationships. The capacitor selection circuit in the nine-level inverter converts the three output voltage sources of DC–DC power converter into a four-level DC voltage, and the full-bridge power converter further converts this four-level DC voltage into a nine-level AC voltage. In this way, the proposed system can generates a sinusoidal output current that is in phase with the utility voltage and is fed into the utility. The salient features of the proposed nine-level inverter are that only seven power electronic switches are used. The proposed concepts have been verified by MATLAB simulations. **Keywords-** Distribution System, Multilevel inverter

# I. Introduction

Now a days, there is a large scarcity of electric energy in our world and at the same time the demand is also increases. Many distributed power system have been developed to meet this high demand by using renewable energy resources like solar systems, wind energy systems and other distributed energy resources[1]. Photovoltaic technology currently being the most popular solar power technology gives rise to a reliable DC power generation source. The solar energy is becoming more important because it produces less pollution. The cost of fossil fuel is increasing, while the cost of solar arrays is decreasing. Recently small capacity distributed power generation systems using photovoltaic energy may be widely used in residential applications [2]. Photovoltaic system is interconnected to a grid through two power stages, dc-dc converter and dc-ac converter [3]-[4]. Power electronic converters, especially dc/ac PWM converters have been extending their range of use in industry because they provide reduced energy consumption, better system efficiency, improved quality of product, good maintenance and so on. The output voltage of a PV array is low; a dc-dc power converter is used in a solar photovoltaic system to boost the output voltage. Fig.1 shows the power conversion process. It should be insure that there is no waste of the energy generated by the PV array because of the important of power conversion efficiency of the power conversion interface. There are mainly two power losses such as conduction losses and switching losses [4]. Conduction loss is due to the use of active devices, and the switching loss is proportional to the voltage changes and the current changes for every switching and switching frequency. For a multilevel inverter, the voltage change in each switching operation is reduced for improving its power conversion efficiency and the switching stress of the active devices [6]-[14].

Multi-level power converter is used to provide more than two voltage levels for achieving less distorted and smoother dc to ac power conversion and it can generate a multiple step voltage waveform with less switching frequency and higher efficiency. A multilevel inverter is a power electronic device that generates a desired output voltage from several levels of dc voltages as input [16]. When the number of input dc voltage sources is increases, the output voltage waveform approaches a nearly sinusoidal waveform. The main advantages of multi level inverter are its higher output quality, lower harmonic component, better electromagnetic computability, and lower switching losses [6]. There are different multilevel inverter topologies have been proposed. The two most common topologies are the cascaded H bridge inverter [10], [15] and the Diode-clamped inverter [7]-[9]. The main advantage of both these topologies is that the rating of the switching devices is highly reduced to the rating of each cell. But the main drawback of these inverters are they require large number of switching devices which equals 2(N-1) where N is the number of levels. This number of switches is very high and which may increases the circuit complexity, and reduce its efficiency. In cascaded Hbridge inverter, the dc link voltage unbalancing problem does not occur, thus easily expanded to multilevel. Due to these advantages, cascaded H-bridge inverter has been widely applied to applications such as HVDC, SVC, stabilizers, and high power motor drives. Apart from these, a multilevel power converter has been introduced as an alternative for high power and medium voltage situations such as laminators, mills, conveyors, pumps, fans, compressors and so on. Multilevel converter not only achieves high power ratings, but also enables the use of

low power application in renewable energy sources such as photovoltaic, wind and fuel cells which can be easily interfaced to a multilevel converter system for a high power application [16].

This paper proposes a new Nine Level Inverter for a photovoltaic system. The nine level inverter is configured using a capacitor selection circuit and a full-bridge power converter, connected in cascade. The inverter contains only seven power electronic switches, which simplifies the circuit configuration. The proposed inverter reduced the switching losses (because of all switches operate with fundamental frequency), complexity and control circuit. The output voltage of a PV array is low; a dc–dc power converter is used to boost the output voltage of the PV array. The output waveforms of multilevel inverters are in a stepped form; therefore they have reduced harmonics compared to a square wave inverter.

#### II. Study of Proposed System

The proposed photovoltaic system is composed of a PV array, a dc-dc power converter, and a new nine-level inverter. Fig.2. shows the configuration of the proposed photovoltaic system. The PV cell array is connected to the dc-dc power converter. The dc-dc power converter is a boost converter that incorporates a transformer with a turn's ratio of 2:1:1.The dc-dc power converter converts the output power of the PV array into three independent voltage sources with multiple relationships, which are supplied to the nine-level inverter. This new nine-level inverter is composed of a capacitor selection circuit and a full-bridge power converter, connected in a cascade. The power electronic switches of capacitor selection circuit determine the discharge of the three capacitors and the three capacitors are being discharged individually or in series. Due to the multiple relationships between the voltages of the dc capacitors, the capacitor selection circuit outputs a four level dc voltage. The full-bridge converter converts this four -level dc voltage to a nine-level ac voltage that is synchronized with the utility voltage. In this way, the proposed photovoltaic system generates a sinusoidal output current that is in phase with the utility voltage and is fed into the utility, and therefore, the power factor become unity. The main advantage of this new nine-level inverter is that it contains only seven power electronic switches, therefore power circuit is become simplified.

Fig .1.Configuration of the proposed photovoltaic system

## 2.1. DC-DC Power Converter

The DC-DC converters can be used as switching mode regulators to convert an unregulated dc voltage to a regulated dc output voltage. The regulation is normally achieved by PWM at a fixed Frequency and the switching device is generally BJT, MOSFET or IGBT. There are several different types of dc-dc converters, buck, boost, buck-boost and cuk etc. Buck converters will produce ripples on the PV module side currents and thus require a larger value of input capacitance on the module side. On the other hand, boost Converters produces low ripple on the PV module side, so in this experimental work, boost converter is used to verify the outputs. Here the DC–DC power converter consists of a boost converter and a current-fed forward converter. A boost converter is a switch mode power supply that has an output voltage higher than its input voltage. The switching in a boost converter is done through a MOSFET or IGBT. When the switch is closed the current flows in the first loop only, and the current through the inductor grows. The switch then opens, and the voltage across the inductor and the input combine in series to charge up the output capacitor to a higher voltage than the input.

IOSR Journal of Electrical and Electronics Engineering (IOSR-JEEE) e-ISSN: 2278-1676,p-ISSN: 2320-3331, PP 15-22 www.iosrjournals.org

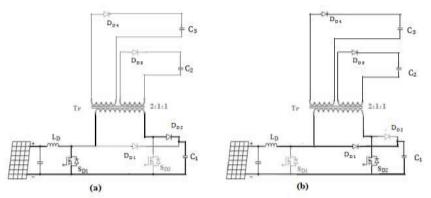

In the proposed system, boost converter is consists of an inductor LD, a power electronic switch SD1 and a diode DD1. The boost converter charges capacitor C1 of the nine-level inverter. The current-fed forward converter is consists of an inductor LD, power electronic switches SD1 and SD2, a transformer, and diodes DD2, DD3 and DD4. The current-fed forward converter charges capacitor C2 and C3 of the nine-level inverter. Fig. 2(a) and fig.2 (b) shows the operating circuit of the dc–dc converter when SD1 is turned ON and SD1 is turned OFF respectively. When SD1 is turned on, the PV cell array C3 are charged in parallel by using the transformer, the voltage ratio of capacitors is the same as the turn ratio (2:1:1) of the transformer. Therefore, the voltages of C1, C2 and C3 have multiple relationships. The voltage of C1, C2 and C3 can be represented as supplies energy to the inductor LD. When SD1 is turned OFF, then SD2 is turned ON and the energy of inductor LD and the PV array charge capacitor C1 through diode DD1 and charge capacitor C2 and C3 through the transformer, the voltage ratio of capacitors is the same as the turn ratio (2:1:1) of the transformer. Therefore, the voltages of C1, C2 and C3 are charged in parallel by using the transformer and diode DD3 and DD4 respectively. Since capacitors C1, C2 and C3 are charged in parallel by using the transformer, the voltage ratio of capacitors is the same as the turn ratio (2:1:1) of the transformer. Therefore, the voltages of C1, C2 and C3 have multiple relationships. The voltage of C1, C2 and C3 are charged in parallel by using the transformer, the voltage ratio of capacitors is the same as the turn ratio (2:1:1) of the transformer. Therefore, the voltages of C1, C2 and C3 have multiple relationships. The voltage of C1, C2 and C3 are charged in parallel by using the transformer, the voltage ratio of capacitors is the same as the turn ratio (2:1:1) of the transformer. Therefore, the voltages of C1, C2 and C3 have multiple relationships. The voltage of C1, C2 an

$$V_{C1} = \frac{1}{(1-D)} V_{s} \dots \dots (1)$$

$$V_{C2} = \frac{1}{2(1-D)} V_{s} \dots \dots (2)$$

$$V_{C3} = \frac{1}{2(1-D)} V_{s} \dots \dots (3)$$

Where Vs is the output voltage of PV array and D is the duty ratio of switch Sd1.

Fig.2. Operation of DC-DC power converter: (a) SDI is ON and (b) SDI is OFF.

The magnetizing inductance of the transformer is increases when SD2 is ON. Conventionally, the forward converter requires a third demagnetizing winding in order to discharge the energy stored in the magnetizing inductance back to the source. But, in the proposed dc–dc converter, when SD2 is turned OFF, the energy stored in the magnetizing inductance is delivered to capacitor C1 through DD2 and SD1 and not back to the dc source, the power efficiency is improved. And also the charging circuits for capacitors C1, C2 and C3are integrated, so the power circuit is simplified.

## 2.2. Nine-Level Inverter

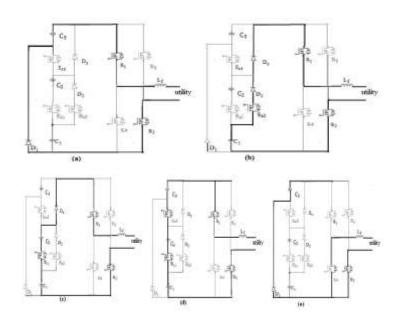

The nine-level inverter is consists of a capacitor selection circuit and a full-bridge power converter, which are connected in cascade. The operation of the nine level inverter can be divided into the positive half cycle and the negative half cycle of the utility. For the analysis, the power electronic switches and diodes are assumed to be ideal. Let Vdc be the total output voltage of the DC-DC converter. The voltages of capacitors C1 , C2 and C3 in the capacitor selection circuit are constant and equal to 2Vdc /4, Vdc /4 and Vdc /4 respectively. The operation of the nine-level inverter in the positive half cycle of the utility can be further divided into five modes, as shown in Fig. 3.

Fig.3.Operation of the nine-level inverter in the positive half cycle (a)mode 1,(b) mode 2, (c) mode 3, (d) mode 4 and (e) mode 5

**Mode 1**: The operation of mode 1 is shown in Fig. 3(a) All the switches of the capacitor selection circuit are OFF, so  $C_3$  is discharged through  $D_1$  and the output voltage of the capacitor selection circuit is  $V_{dc}/4$  and  $S_1$  and  $S_2$  of the full-bridge power converter are ON. At this point, the output voltage of the nine-level inverter is directly equal to the output voltage of the capacitor selection circuit, which means the output voltage of the nine-level inverter is  $V_{dc}/4$ .

**Mode 2**: The operation of mode 2 is shown in Fig. 3(b). In the capacitor selection circuit,  $S_{S2}$  is ON,  $S_{S1}$  and  $S_{S3}$  are OFF. So  $C_1$  is discharged through  $S_{S2}$ ,  $D_2$  and  $D_3$  and the output voltage of the capacitor selection circuit is  $2V_{dc}/4$  and  $S_1$  and  $S_2$  of the full-bridge power converter are ON. At this point, the output voltage of the nine-level inverter is  $2V_{dc}/4$ .

**Mode 3**: The operation of mode 3 is shown in Fig. 3(c). In the capacitor selection circuit,  $S_{S1}$  is ON,  $S_{S2}$  and  $S_{S3}$  are off. Both  $C_1$  and  $C_2$  are discharged in series and the output voltage of the capacitor selection circuit is  $3V_{dc}/4$  and  $S_1$  and  $S_2$  of the full-bridge power converter are ON. At this point, the output voltage of the nine-level inverter is  $3V_{dc}/4$ .

**Mode 4**: The operation of mode 4 is shown in Fig. 3(d). In the capacitor selection circuit,  $S_{S1}$  and  $S_{S3}$  are ON,  $S_{S2}$  is off. Capacitors  $C_1$ ,  $C_2$  and  $C_3$  are discharged in series and the output voltage of the capacitor selection circuit is  $V_{dc}$  and  $S_1$  and  $S_2$  of the full-bridge power converter are ON. At this point, the output voltage of the nine-level inverter is  $V_{dc}$ .

**Mode 5**: The operation of mode 5 is shown in Fig. 3(e). All the switches of the capacitor selection circuit are OFF. The output voltage of the capacitor selection circuit is  $V_{dc}$  /4. Only  $S_2$  of the full-bridge power converter is ON. Since the output current of the nine-level inverter is positive and passes through the filter inductor, it forces the anti parallel diode of  $S_4$  to be switched ON for continuous conduction of the filter inductor current. At this point, the output voltage of the nine-level inverter is zero. Therefore, in the positive half cycle, the output voltage of the nine-level inverter has five levels:  $V_{dc}$ ,  $3V_{dc}$  /4,  $2V_{dc}$  /4 and 0.

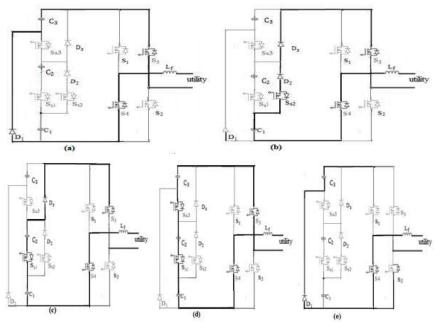

In the negative half cycle, the output current of the nine-level inverter is negative. The operation of the nine-level inverter can also be divided into five modes, as shown in Fig.4. The operation of the capacitor selection circuit in the negative half cycle is the same as that in the positive half cycle. The difference is that  $S_3$  and  $S_4$  of the full-bridge power converter are ON during modes 6, 7, and 8, 9 and S4 is also ON during mode 10 of the negative half cycle. Therefore, the output voltage of the capacitor selection circuit is inverted by the full-bridge power converter, so the output voltage of the nine-level inverter also has five levels:  $-V_{dc}$ ,  $-3V_{dc}$ , /4,  $-2V_{dc}$ , /4,  $-V_{dc}$ , /4, -0,  $-V_{dc}$ , /4,  $-2V_{dc}$ , /4,

Fig.4. Operation of the nine-level inverter in the negative half cycle (a)mode 6,(b) mode 7, (c) mode 8, (d) mode 9 and (e) mode10.

Since only seven power electronic switches are used in the proposed nine-level inverter, the power circuit is significantly simplified compared with a conventional nine level inverter. It can be seen that the change in the output voltage of the nine-level inverter for each switching operation is Vdc/4, so switching power loss is reduced.

## III. Simulation Results And Analysis

The simulation and verification of Nine- Level Inverter technique is done in Matlab//Simulink Software.

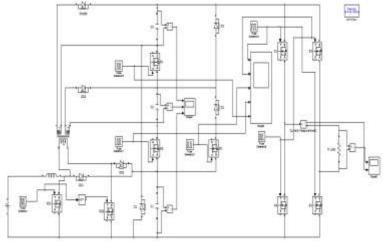

Fig. 5.Simulation model for a proposed system

The simulation model in the fig.5 consists of a DC power supply, DC-DC converter and a nine level inverter. Instead of solar cell, DC source is used as DC supply. The supply is given to a DC -DC converter and the converter converts the output power of the DC source into three independent voltage sources with multiple relationships, which are supplied to the nine-level inverter .Simulation parameters are given in the table I.

#### TABLE 1

| Simulation parameters |             |  |  |  |

|-----------------------|-------------|--|--|--|

| Parameters            | Value       |  |  |  |

| Power Supply          | 10V         |  |  |  |

| Capacitor             | 1000µF      |  |  |  |

| Load Resistor         | 1ΚΩ         |  |  |  |

| Inductor              | 1mH         |  |  |  |

| Transformer           | 2:1:1 ratio |  |  |  |

| MOSFET                |             |  |  |  |

| Diode                 |             |  |  |  |

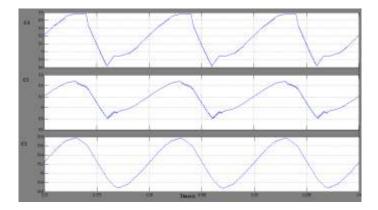

Fig.6.shows the voltages across capacitors C1, C2 and C3 of the capacitor selection circuit.

Fig.6.voltages across capacitors C1, C2 and C3

For an input voltage of 10V, figure 6 shows that the voltages of capacitors C<sub>1</sub>, C<sub>2</sub> and C<sub>3</sub> of the capacitor selection circuit have multiple relationships and are maintained nearer to 20V, 10V, and 10V respectively. Fig.7.shows the output voltage and current waveform of the nine- level inverter.

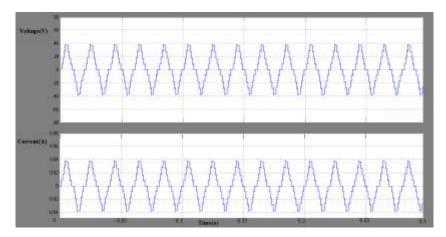

Fig.7.output voltage and current waveform

Figure shows that the output voltage of the nine-level inverter has nine voltage levels (0V, 10V, 20V, 30V, 40V, -10V,-20V,-30V,-40V). This voltage will be varied according to the voltage across the capacitor selection circuit. Maximum voltage in the output of nine level inverter depends on the output voltage of capacitor selection circuit. The total harmonic distortion (THD) of output of the nine level inverter is 2.73%. Since only seven power electronic switches are used in the new nine-level inverter, the power circuit is significantly simplified compared with a conventional nine-level inverter. The states of the power electronic switches of the nine-level inverter, as detailed previously, are summarized in Table II.

TABLE II

States Power Electronic Switches

IOSR Journal of Electrical and Electronics Engineering (IOSR-JEEE) e-ISSN: 2278-1676,p-ISSN: 2320-3331, PP 15-22 www.iosrjournals.org

| Voltage Levels                 | States Power Electronic Switches |                 |                 |                |                       |                |                |  |

|--------------------------------|----------------------------------|-----------------|-----------------|----------------|-----------------------|----------------|----------------|--|

|                                | S <sub>S1</sub>                  | S <sub>S2</sub> | S <sub>S3</sub> | S <sub>1</sub> | <b>S</b> <sub>2</sub> | S <sub>3</sub> | S <sub>4</sub> |  |

| V <sub>dc</sub>                | 1                                | 0               | 1               | 1              | 1                     | 0              | 0              |  |

| $3V_{dc}/4$                    | 1                                | 0               | 0               | 1              | 1                     | 0              | 0              |  |

| 2V <sub>dc</sub> /4            | 0                                | 1               | 0               | 1              | 1                     | 0              | 0              |  |

| $V_{dc}/4$                     | 0                                | 0               | 0               | 1              | 1                     | 0              | 0              |  |

| 0                              | 0                                | 0               | 0               | 0              | 1                     | 0              | 0              |  |

| 0                              | 0                                | 0               | 0               | 0              | 0                     | 0              | 1              |  |

| $-V_{dc}/4$                    | 0                                | 0               | 0               | 0              | 0                     | 1              | 1              |  |

| $\frac{-V_{dc}/4}{-2V_{dc}/4}$ | 0                                | 1               | 0               | 0              | 0                     | 1              | 1              |  |

| $-3V_{\rm dc}/4$               | 1                                | 0               | 0               | 0              | 0                     | 1              | 1              |  |

| V <sub>dc</sub>                | 1                                | 0               | 1               | 0              | 0                     | 1              | 1              |  |

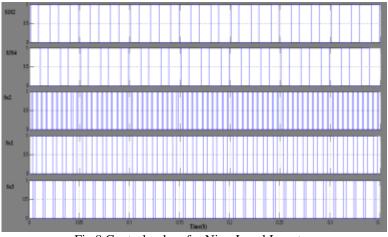

According to the states of power electronic switches, different control pulses can be generated for a time period of 20ms (frequency 0f 50Hz) and shown in fig.9.

Fig.8.Control pulses for Nine-Level Inverter

First pulse shows the gate signal for  $S_1$  and  $S_2$  in the nine level inverter. When S1 and S2 are ON, at that time  $S_3$  and  $S_4$  are OFF. In the positive half cycle,  $S_1$  and  $S_2$  are ON and in the negative half cycle  $S_3$  and  $S_4$  are ON. Second pulse shows the gating signal for  $S_3$  and  $S_4$ . Switching pulses of  $Ss_1$ ,  $Ss_2$  and  $Ss_3$  are determines the different voltage levels in the nine-level inverter. Third figure shows the gating signal for  $Ss_2$ . When  $Ss_2$  is ON, the output voltage become  $2V_{dc}/4$  and  $-2V_{dc}/4$ . Fourth figure shows the gating signal for  $Ss_3$ . When  $Ss_1$  is ON, the output voltage become  $3V_{dc}/4$  and  $-3V_{dc}/4$ . Fifth figure shows the gating 6 signal for  $Ss_3$ . When  $Ss_3$  is ON, the output voltage become  $V_{dc}$  and  $-V_{dc}$ .

#### IV. Conclusion

This paper is based on a Nine-Level Inverter for a photovoltaic system. The DC energy generated by the photovoltaic system is converted to AC energy and that is fed into the utility grid. Due to the low output voltage of the PV system, a DC-DC converter is used to boost the output voltage, so it can be match the DC output voltage of the inverter. Then a nine-level inverter is used to convert this DC voltage into AC voltage and fed into utility. The nine level inverter is configured using a capacitor selection circuit and a full-bridge power converter, connected in cascade. The capacitor selection circuit consists of three capacitors and they charged in parallel by using a transformer and the voltage ratio of the capacitors is the same as the turn's ratio of the transformer. So the power circuit is simplified. Because of the multiple relationships between the voltages of the inverter further converts this four -level dc voltage to a nine-level ac voltage that is synchronized with the utility voltage. The inverter contains only seven power electronic switches, which simplifies the circuit configuration. As compared to ordinary inverter, the voltage change in each switching operation for a multilevel inverter is reduced, so that the proposed inverter reduces the switching losses, complexity of the circuit. The output waveforms of

IOSR Journal of Electrical and Electronics Engineering (IOSR-JEEE) e-ISSN: 2278-1676,p-ISSN: 2320-3331, PP 15-22 www.iosrjournals.org

multilevel inverters are in a stepped form; therefore they have reduced harmonics compared to a square wave inverter.

#### References

- R. Dugan, T. McDermott, "Distributed generation," IEEE Ind. Appl. Mag., vol. 8, no. 2, pp. 19-25, Mar./Apr. 2002. [1]

- R. A. Mastromauro, M. Liserre, and A. Dell'Aquila, "Control issues in single-stage photovoltaic systems: MPPT, current and [2] voltage control," IEEE Trans. Ind. Informat., vol. 8, no. 2, pp. 241–254, May. 2012. N. Mohan, T. M. Undeland, and W. P. Robbins, "Power Electronics Converters, Applications and Design", Media Enhanced 3rd

- [3] ed. New York, NY, USA: Wiley, 2003.

- .[4] J.-M. Shen, H. L. Jou, and J. C. Wu, "Novel transformer-less grid connected power converter with negative grounding for photovoltaic generation system," IEEE Trans. Power Electron., vol. 27, no. 4, pp. 1818–1829, Apr. 2012.

- Jinn-Chang Wu, Member, IEEE, and Chia-Wei Chou," A Solar Power Generation System With a Seven-Level Inverter", IEEE [5] Trans. on power electronics, vol. 29, no. 7, july 2014

- [6] K. Hasegawa and H. Akagi, "Low-modulation-index operation of a five level diode-clamped pwm inverter with a dc-voltagebalancing circuit for a motor drive," IEEE Trans. Power Electron., vol. 27, no. 8, pp. 3495-3505, Aug. 2012.

- E. Pouresmaeil, D. Montesinos-Miracle, and O. Gomis- Bellmunt, "Control scheme of three-level NPC inverter for integration of [7] renewable energy resources into AC grid," IEEE Syst. J., vol. 6, no. 2, pp. 242-253, Jun. 2012.

- S. Srikanthan and M. K. Mishra, "DC capacitor voltage equalization in neutral clamped inverters for DSTATCOM application," IEEE Trans. Ind. Electron., vol. 57, no. 8, pp. 2768–2775, Aug. 2010 [8]

- N. A. Rahim, K. Chaniago, and J. Selvaraj, "Singlephase seven-level grid-connected inverter for photovoltaic system," IEEE [9] Trans. Ind. Electr., vol. 58, no. 6, pp. 2435–2443, Jun. 2011.

- S. Thielemans, A. Ruderman, B. Reznikov, and J. Melkebeek, "Improved natural balancing with modified [10] phase-shifted PWM for single-leg fivelevel flying-capacitor converters," IEEE Trans. Power Electron., vol. 27, no. 4, pp. 1658-1667, Apr. 2012.

- [11] S. Choi and M. Saeedifard, "Capacitor voltage balancing of flying capacitor multilevel converters by space vector PWM," IEEE Trans. Power Delivery, vol. 27, no. 3, pp. 1154 1161, Jul. 2012.

- [12] L. Maharjan, T. Yamagishi, and H. Akagi, "Activepower control of individual converter cells for a battery energy storage system based on a multilevel cascade pwm converter," IEEE Trans. Power Electron., vol. 27, no. 3, pp. 1099-1107. Mar. 2012.

- [13] X. She, A. Q. Huang, T. Zhao, and G. Wang, "Coupling effect reduction of a voltage-balancing controller

- in single-phase cascaded multilevel converters," IEEE Trans. Power Electron., vol. 27, no. 8, pp. 3530-3543, Aug.2012.

- J. Chavarria, D. Biel, F. Guinjoan, C. Meza, and J. J. Negroni, "Energy balance control of PV cascaded multilevel grid-connected inverters under level-shifted and phaseshifted PWMs," IEEE Trans. Ind. Electron., vol. 60, no. 1, pp. 98–111, Jan. 2013. [14]

- [15] J. Mei, B. Xiao, K. Shen, and L. M. Jian Yong Zheng, "Modular multilevel inverter with new modulation method and its application to photovoltaic grid-connected generator," IEEE Trans. Power Electron., vol. 28, no. 11, pp. 5063-5073, Nov. 2013.